# The Solaris Operating System on x86 Platforms

Crashdump Analysis Operating System Internals

# **Table of Contents**

| 1.Foreword                                                  | 5   |

|-------------------------------------------------------------|-----|

| 1.1.History of this document                                | 5   |

| 1.2.About modifying this document                           | 7   |

| 2.Introduction to x86 architectures                         | 9   |

| 2.1.History and Evolution of the x86 architecture           |     |

| 2.2.Characteristics of x86                                  |     |

| 2.3.Marketeering – Naming the architecture                  | 19  |

| 3.Assembly Language on x86 platforms                        | 21  |

| 3.1.Generic Introduction to Assembly language               |     |

| 3.2.Assembly language on x86 platforms                      | 25  |

| 3.3.x86 assembly on UNIX systems – calling conventions, ABI |     |

| 3.4.Case study: Comparing x86 and SPARC assembly languages  |     |

| 3.5.The role of the stack                                   | 46  |

| 3.6.Odd things about the x86 instruction set                | 50  |

| 3.7.Examples of compiler-generated code on x86 platforms    | 51  |

| 3.8.Accessing data structures                               | 65  |

| 3.9.Compiler help for debugging AMD64 code                  | 73  |

| 4.Memory and Privilege Management on x86                    | 77  |

| 4.1.The x86 protected mode – privilege management           | 78  |

| 4.2.Traps, Interrupts, System Calls, Contexts               |     |

| 4.3.Virtual Memory Management on x86                        | 91  |

| 4.4.Advanced System Programming Techniques on x86           | 101 |

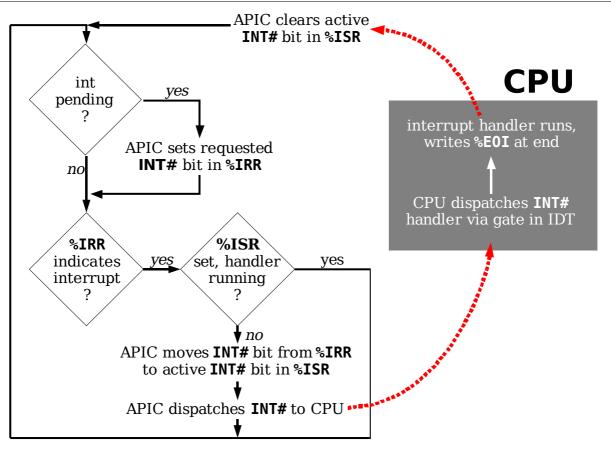

| 5.Interrupt handling, Device Autoconfiguration              |     |

| 5.1.Interrupt Handling and Interrupt Priority Management    | 103 |

| 5.2.APIC and IOAPIC features                                | 104 |

| 6.Solaris/x86 architecture                                  | 111 |

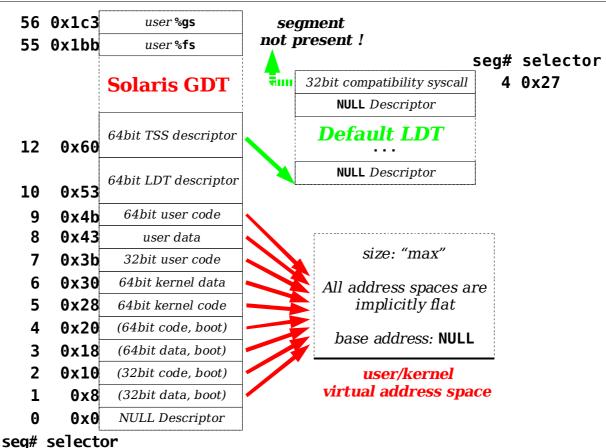

| 6.1.Kernel and user mode                                    | 112 |

| 6.2.Entering the Solaris/x86 kernel                         |     |

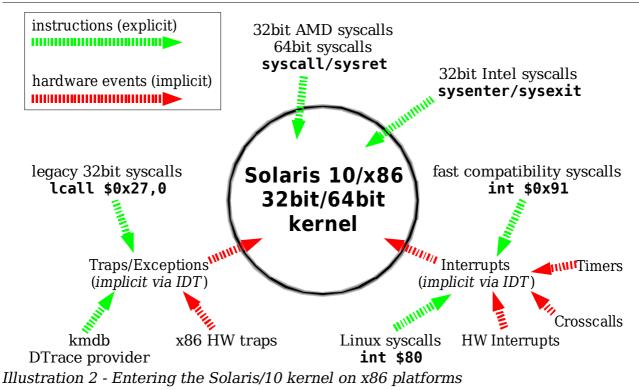

| 6.3.Solaris/x86 VM architecture – x86 HAT layer             |     |

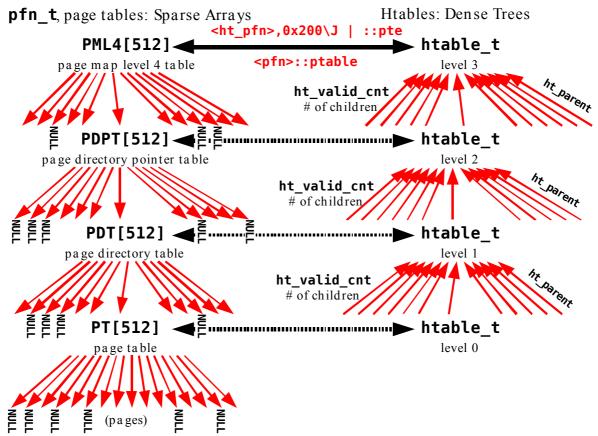

| 6.4.Virtual Memory Layout                                   | 121 |

| 6.5.Context switching                                       |     |

| 6.6.Supporting Multiple CPUs                                |     |

| 6.7.isaexec – Creating 32/64bit-specific applications       | 125 |

| 7.Solaris/x86 Crashdump Analysis                            | 127 |

| 7.1.Debugging tools for core-/crashdump analysis            |     |

| 7.2.Troubleshooting system hangs on Solaris/x86             |     |

| 7.3.32bit kernel crashdump analysis – a well-known example  |     |

| 7.4.64bit kernel crashdump analysis – well known example    |     |

| 7.5.Another 64bit crashdump analysis example                |     |

| 7.6.AMD64 ABI – Backtracing without framepointers           | 176 |

| 10.License                                                   |     |

|--------------------------------------------------------------|-----|

| 9.References                                                 |     |

| 8.2.Stacks and Stacktracing                                  |     |

| 8.1.Introduction to x86 assembly language                    |     |

| 8.Lab Exercises                                              |     |

| 7.8.Advanced Debugging Topics                                | 178 |

| 7.7.Examples on application coredump analysis on Solaris/x86 | 177 |

# 1.Foreword

## 1.1.History of this document

This document didn't start out from nowhere, but neither has it originally been intended for publication in book form. But then, sometimes history takes unexpected paths ...

Shortly after Sun had revised the ill-begotten idea of "phasing out" Solaris for x86 platforms and started to ramp up a hardware product line with Intel CPUs in it. I was approached by the Service division within Sun about where they could get an introductory course about how to perform low-level troubleshooting – crashdump analysis – on the x86 platform. Information and trainings about troubleshooting on this level on SPARC platforms are widely available - starting with the famous "Panic!" book all the way to extensive classes offered by Sun Educational Services to participants both internal and external to Sun. That notwithstanding, we soon found out that no internal training about the low-level guts of Solaris/x86 did exist. Development engineers were usually both capable and encouraged to find out about the x86 platform on their own, and users outside of the engineering space were few and far between. So this project started as a slide set for teaching engineers who were familiar with SPARC assembly, Solaris Internals and some Crashdump Analysis the fundamentals of x86 assembly and Solaris on x86 platforms, strongly focusing on "what's similar" and "what's different" between the low-level Solaris kernel on SPARC and x86 platforms.

I was to a large degree surprised by the amount of interest this material generated internally, so it grew, as time allowed, into a multi-day internal course on Solaris/x86 internals and crashdump analysis. For a while, I came to spend a significant amount of time teaching this never-official "class" ...

Then came the work on Solaris 10 and the AMD64 port. The new "64bit x86" platform support brought changes in the ABI with it that severely surprised even experienced "x86 old-timers" and required a large amount of addition to the existing material, which at that time had grown into a braindump of semi-related slides. Revamping the Solaris hardware interface layer for both 32bit and 64bit on x86/AMD64 as well as the addition of new features like Dtrace or the Linux Application Environment made further modifications necessary.

In the end, StarOffice's limited ability to deal with presentations of 200+ slides eventually made it inevitable to drop the till-then adapted method of "add a slide as a new question comes up".

Would I have to make the same choice again I'd probably have opted to install myself a TeX system, but I decided to give StarOffice another chance and turn this material into something closer to a book. How I regret not having used TeX to start with ... that'll teach me !

Over the course of the AMD64 port of Solaris this grew into essentially the current form, and when people started using the 64bit port internally a large amount of new questions and typical problems came up which I attempted to address. To say it upfront, while the assembly language on AMD64 will be immediately familiar to people who know about "classical" x86, the calling conventions used in 64bit machine code on AMD64 are so much different that in many aspects crashdump analysis on Solaris/AMD64 is closer to Solaris/SPARC than it is to Solaris/x86. But then it isn't ... well, I'm disgressing, go read the book.

Then the OpenSolaris project came. Initially, I had planned to publish this on launch

day, but for many reasons this didn't work out at that time. So here it is – several months delayed, no longer completely covering the state of our internal and external (OpenSolaris) development releases. But it's finally reviewed, the crashdump analysis example dumps are made available, the StarOffice document has been cleaned up to only rely on freely available fonts + graphics.

Which means that *you* – yes, look into the mirror – are now supposed to work with this material, *and on it*. The whole document including all illustrations are now made available in editable form.

Please read the license attached to the end of the document.

- Yes, you can make modifications to this document.

- Yes, you can redistribute copies of this document in any form you see fit you're in fact encouraged to do so.

- Yes, you're encouraged to contribute corrections or additions.

For all else legalese, see the appendix.

© 2003-2005, Frank Hofmann, Sun Microsystems, Inc.

Enjoy – and never forget:

(Shall I say green is my favourite color ?)

If you wish to contact the author, please send Email to:

Frank.Hofmann@sun.com

At this point in time, I cannot even start listing the number of people that have made this document possible. Given that it didn't start as a book project I've kept a lousy bibliography.

I'd like to both thank every unnamed contributor as well as excuse myself for not naming you.

Using the words of Isaac Newton:

# *"If I have seen further it is by Standing on the shoulder of giants."*

You know who you are.

## **1.2.About modifying this document**

StarOffice8 is used to edit this document, but (Beta) versions of OpenOffice 2.x should be able to access it as well.

The document uses the OpenSource *DejaVu* fonts which are a derivative of BitStream Vera. The difference between these two is that the DejaVu font family contains full **bold**/*italic*/condensed typefaces for Sans, Serif and Monospaced, while the original Bitstream Vera fonts only supply the full typeface set for Sans. Installing the DejaVu fonts is therefore a prerequisite to being able to edit this document and recreate the output as-is.

These fonts are available from http://dejavu.sourceforge.net

Other fonts than DejaVu should not be used. To simplify this, switch the StarOffice stylist tools to only show "Applied Styles", and don't use any but these.

If you wish to contribute back changes/additions in plain text that's more than welcome. If you modify the StarOffice document itself, allow simple merge back by enabling the change recording facility in StarOffice. See the help functionality, on "Changes".

Note that StarOffice's master text facility is somewhat dumb – it records full pathnames (instead of relative locations) for the subdocuments. When you open **book.odm** in StarOffice8, the Navigator will show you the list of subdocuments. Use the right mousebutton to request the context menu, and choose "Edit Link" to change the pathnames of the subdocuments to refer to the location where you unpacked the file set.

The same is true for embedding graphics. Not even the documented functionality ("link" to the illustrations instead of instantiate a copy for the document) is working. So be aware when you change some file under **figures**/, you might need to delete and reinsert it in the main document ...

I'll keep a pointer to the current version (StarOffice for editing / PDF for reading and printing) of this document on my blog:

http://blogs.sun.com/ambiguous/

And finally: These instructions should be better ...

## 2.Introduction to x86 architectures

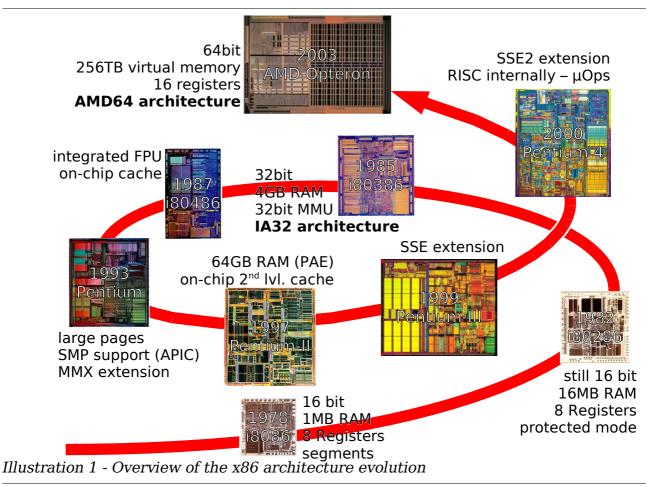

## 2.1. History and Evolution of the x86 architecture

The main driving force in development of the x86 processor family has always been to enhance existing functionality in such a way that full binary-level compatibility with previous x86 processors can be maintained. How important this is to Intel is best described in Intel's own words:

#### One of the most important achievements of the IA-32 architecture is that the object code programs created for these processors starting in 1978 still execute on the latest processors in the IA-32 architecture family.

Among all CPU architectures still available in current machines, only the IBM3xx mainframe architecture (first introduced in 1964 with the IBM360, still available in the IBM zSeries mainframes) has a longer history of unbroken binary backward compatibility. All current "x86-compatible" CPUs still support and implement the full feature set of the original member of the x86 family, the Intel 8086 CPU which was introduced in 1978.

This means: Executable programs from code originally written for the 8086 will run unmodified on any recent x86-compatible CPU such as Intel's Pentium-IV or AMD's Opteron processor. Yes, MSDOS 1.0 is quite likely to run on the very latest and greatest "PC-compatible", provided you can still find some single-sided 360kB 5<sup>1</sup>/<sub>4</sub>"

floppy drive which would allow you to boot it on that shiny new AMD Opteron workstation.

Backward compatibility of the x86 processor family goes way beyond what most other CPU architectures (including SPARC) have to offer. Sun Microsystem's Solaris/SPARC binary compatibility guarantee only ensures that *applications* (not operating systems or other low-level code) written on and for previous OS/hardware will continue to run on recent OS/hardware combinations, but it does not claim that old versions of the Solaris Operating Environment will run on processors that were yet unreleased at the time a specific release shipped. This is different on x86. New versions of x86 CPUs from whatever vendor run older operating systems just fine. Incompatibilities if at all rise from the lack of device driver support for newer integrated peripherals, but not from the newer CPU's inability to function like its predecessors.

Since introduction of the Intel i80386 in 1985 (!), most features of the x86 architecture have remained remarkably constant. SMP support (via APIC) and support for more than 4GB physical memory (via PAE) was added in the Pentium respectively to the PentiumPro processors; after that, only instruction set extensions (MMX, SSE) were added but no externally-visible changes were done to other core subsystems of x86.

From the point of view of Solaris/x86, it was never necessary therefore to have more than one kernel, **/platform/i86pc/kernel/unix**, for supporting the operating system on x86 processors. Put this in context and compare it with Solaris in SPARC: For the various SPARC generations (maximum number of architectures concurrently supported in Solaris 2.6: sun4, sun4c, sun4d, sun4m, sun4u, sun4u1), each time separate platform support was required. Even today, Solaris 9 delivers ten (!) different kernels for the various SPARC platforms, while Solaris 9 for x86 still has only one.

This strict insistence on binary compatibility with its predecessors obviously has disadvantages as well. The way how the i80386 introduced 32bit support in some areas looks illogical and counterintuitive, especially when comparing it with 32bit architectures that were designed for 32bit from their very beginnings. Some examples of this will be given later.

After releasing the i80386 32bit processor, Intel decided to keep future versions of x86-compatible ("IA32" in Intel's terms) CPUs on 32bit. Each generation became faster and added functionality, but the limitation to 32bit remained. In the early 1990s, this did not seem a problem because the major markets for x86 at that time (Microsoft DOS and Windows) were 16bit only anyway, and Intel's evolutionary path to 64bit had been layed out in the agreement with HP to co-develop a new 64bit architecture: IA64, then dubbed "Merced", is today found in the Intel Itanium processors.

But IA64 has nothing to do with x86. The instruction sets have nothing in common and existing programs or operating systems written for 32bit x86 processors cannot run on machines with IA64/Itanium processors in it. The Itanium, though produced by Intel, is a genetic child of HP's PA-RISC architecture, but only a distant relative to Intel's own x86/IA32.

In addition to that, Intel and HP were late at delivering the IA64 CPU – very late.

So late that back in 2000, AMD stepped in and decided to extend the old x86 architecture another time – to 64bit. AMD had, with varying success, been building x86-compatible processors since the early 1980s and saw Intel's de-facto termination of x86 as a chance to extend its own market reach. The AMD64 (64bit x86) architecture was done in a way very similar to how Intel had done the i80386, and processors based on AMD64 (much unlike Itanium/IA64) are, in good old x86 tradition, fully binary backward compatible. Of course, actually using the new 64bit operating mode requires porting operating system and applications (like using 32bit on the

i80386 did require at the time). But even when running a 64bit operating system does AMD64 provide a sandboxed 32bit environment to run existing applications in (again, like the i80386 which allowed the same for 16bit programs running on a 32bit OS). Therefore the AMD64 architecture offers much better investment protection than IA64 – which will *not* run existing 32bit operating systems or applications.

By the time the AMD Opteron 64bit processor became available, the Itanium, on the market for three years then, had seen very little adoption – while users and software vendors kept pushing ever harder on Intel to follow AMD's lead and provide 64bit capabilities in their x86 processor line as well. Intel resisted this for several years in order not to jeopardize the market for their Itanium processors but eventually gave in and cloned AMD64. For obvious reasons Intel doesn't call their 64bit-capable x86 processors "AMD64-compatible" but uses the term EM64T (*Enhanced Memory 64bit Technology*) for the architecture and IA32e for the 64bit instruction set extension. Intel CPUs with EM64T are compatible to AMD64 – which Intel confirms in the FAQ for the 64bit Extension Technology.

http://www.intel.com/technology/64bitextensions/faq.htm notes that:

Q9: Is it possible to write software that will run on Intel's processors with Intel® EM64T, and AMD's 64-bit capable processors?

**A9**: Yes, in most cases. Even though the hardware microarchitecture for each company's processor is different, the operating system and software ported to one processor will likely run on the other processor due to the close similarity of the instruction set architectures.

How the future of x86 will look remains to be seen. But the x86 architecture, with more than 25 years of age, has far surpassed the success of all other (non-embedded) processor architectures ever developed. With 64bit extensions that have rejuvenated x86, and x86-compatible processors with 64bit capabilities becoming commonplace now, this is unlikely to change in the near future.

## 2.2.Characteristics of x86

There are two factors responsible for the main characteristics of the machine instruction set for what is commonly termed "x86 architecture":

- The long history of x86 has left its mark on the instruction set. x86 machine code carries a huge legacy of (mis-)features from the time when the architecture was still 16bit only, and in parts even from pre-x86 8bit days (in the form of limited compatibility with the Intel 8008).

- The need to introduce new capabilities without breaking binary compatibility has lead to a lot of instruction set extensions that are optional, and whose presence needs to be detected by applications / operating systems that want to make use of them. In addition, x86 never was a vendor-locked-in architecture, even though Intel's decisions have dominated its evolution. Both operating systems and application code for x86 therefore needs to expend some efforts on determining which CPU by what vendor it runs on, and what instruction set extensions this CPU provides before it can make use of optimized code.

This is fortunately much improved by AMD64 which establishes a new "64bit x86 baseline".

In addition to that, x86 CPUs use the so-called *little endian* way of ordering data in memory. Endianness becomes very relevant once data needs to be exchanged between systems of differing architecture.

## 2.2.1.CISC and RISC

Back in the early days of CPU design in the 1970s and early 1980s, manufacturing technology did not allow for anything close to the complexity we have today. CPU designers then had to make tradeoffs, mostly between a feature-rich assembly language, but few registers and generally lower instruction throughput, and a feature-poor assembly language with many registers and faster execution for the simple instructions that there were.

The x86 architecture is the classical example of a so-called CISC processor. The term *CISC* stands for *Complex Instruction Set Computer*, and is used to describe a processor whose instruction set offers single, dedicated CPU instructions for possibly very involved tasks. Philosophically, the ultimate design goal for a CISC processor is to achieve a 1:1 match between CPU instructions and instructions in a high-level programming language.

CISC is almost a requirement for CPUs which maintain full backward compatibility such as the x86 family. Adding functionality to an existing architecture always means adding instructions and complexity. A pure evolutionary CPU development as Intel has done it therefore almost necessitates a CISC architecture.

All in all, Intel's latest instruction set reference needs two volumes and more than 1000 pages to describe all x86 instructions supported by the latest x86 CPUs by Intel. For comparison - the sparcv9 architecture reference manual only has 106 pages describing all sparcv9 assembly instructions.

Given the focus on instruction functionality vs. versatility, CISC architectures tend to have features like:

• many special-purpose instructions.

An example on x86 would be two separate instructions for comparison – the generic **CMP** instruction and the **TEST** instruction which will only check for equality or zeroness.

- the ability to modify a memory location directly, without the need to load its contents into a register first. This is done to offset the lack of registers – the idea is that if destination or source of an operation can be memory, less registers are needed.

- instructions with varying length. This is both due to the fact that CISC architectures usually allow to embed (large) constants into the instruction, and because feature additions over time have required the introduction of longer opcodes (instruction encodings). Another consequence of this is that there are few gaps (undefined or illegal opcodes) in the instruction set. As we will see, to an x86 CPU random data makes up for a decodeable instruction stream !

- few general-purpose registers.

Historically there had to be a tradeoff between using the space on the CPU die to provide more registers or more-capable instructions. CISC CPU designers chose to do the latter, and it often proved difficult to extend the register set even after manufacturing technologies would have allowed for it. The x86 architecture lived with only eight registers, until AMD designing the 64bit mode finally took the chance and extended the register set to 16.

The x86 architecture is the single major remaining CISC architecture out there today. Most other CPU architectures on the market today, whether SPARC, PowerPC, ARM or (to a degree) even IA64, have gone the other way – RISC.

| SPARC assembly source | binary machine code | disassembler output |

|-----------------------|---------------------|---------------------|

| func:                 | section .text       | section .text       |

| tst %i0               | 0: 80 90 00 18      | tst %i0             |

| orcc %g0, %i0, %g0    | 4: 80 90 00 18      | tst %i0             |

| set 1234, %i0         | 8: b0 10 24 d2      | mov 0x4d2,%i0       |

| or %q0, 1234, %i0     | c: b0 10 24 d2      | mov 0x4d2, %i0      |

| cmp %i0, %i1          | 10: 80 a6 00 19     | cmp %i0, %i1        |

| subcc %i0, %i1, %g0   | 14: 80 a6 00 19     | cmp %i0, %i1        |

| clr %i0               | 18: b0 10 00 00     | clr %i0             |

| or %g0, %g0, %i0      | 1c: b0 10 00 00     | clr %i0             |

| mov %i1, %i0          | 20: b0 10 00 19     | mov %i1, %i0        |

| or %g0, %i1, %i0      | 24: b0 10 00 19     | mov %i1, %i0        |

| .size func,func       |                     |                     |

Illustration 1 - machine code example on RISC, synthetic instructions

SPARC and all its incarnations are a classical example of *RISC* (*Reduced Instruction Set Computer*), and share many generic features with other RISC architectures:

- Lots and lots of CPU registers are available. For example, SPARC provides at least 32 general-purpose registers (internally hundreds, via register windows).

- To modify data in memory, one must load it into a register, modify the register contents and store the register back into memory. This is called a *load-store architecture*.

- RISC instructions usually have a fixed instruction size. All SPARC instructions, for example, are 32bit. RISC Instruction sets are rather *designed* than *evolved*.

- Instructions often are multi-purpose. A RISC CPU, for example, may not have separate instructions for subtracting values, comparing values or testing values for zero instead, typically, "SUB" will be used but the result (apart from condition bits) be ignored. See the SPARC assembly code example above.

- Instructions tend to be simple. If a RISC CPU offers complex instructions at all, they

are usually completed by help of the operating system - instructions leading to complex system activity will trap and require software help to finish.

Unlike CISC, the focus for RISC is on raw execution power - the more instructions per unit of time a CPU can process the faster it will be in the end. Executing a dozen simple instructions as fast as theoretically possible often proves to provide better throughput than executing a single, slow instruction to achieve the same effect. RISC originally was invented to allow for simpler CPU designs running at higher clock speed.

RISC pays for this by often requiring more instructions to achieve an equivalent result as CISC gets with just one or two instructions:

| x86 assembly                                           | binary code                                                       | SPARC assembly                                                                                                                                                                                                                            | binary code                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| movq<br>\$0x123456789abcdef0,<br>%rax<br>addq %rax,var | 48 b8<br>f0 de bc 9a<br>78 56 34 12<br>48 01 04 25<br>XX XX XX XX | <pre>sethi %hi(0x12345400), %o1 xor %o1, -0x279, %o1 sethi %hi(0x65432000), %o0 xor %o0, -0x110, %o0 sllx %o1, 32, %o1 xor %o1, %o0, %o0 sethi %hi(var), %o1 or %o1, %lo(var), %o1 ldx [%o1], %o2 addc %o0, %o2, %o2 stx %o2, [%o1]</pre> | 13       04       8d       15         92       1a       7d       87         11       19       50       c8         90       1a       3e       f0         93       2a       70       20         90       1a       40       08         13       0X       XX       XX         92       12       6X       XX         d4       5a       40       00         94       42       00       0a         d4       72       40       00 |

Illustration 2 - RISC & CISC: Adding a 64bit constant to a global variable "var"

Today, most arguments in the CISC vs. RISC debate have become obsoleted by technical progress.

Since the introduction of Intel's Pentium-IV and AMD's Athlon, modern x86 processors internally "recompile" x86 instructions into RISC instruction sets. Intel calls this  $\mu$ -ops, while AMD uses the term ROPs (RISC ops) openly. These RISC execution engines in x86 CPUs are not exposed to the user - the step of decoding/compiling x86 instructions into the underlying micro-ops is done by an additional layer of hardware in the instruction decoder part of these CPUs.

Likewise, RISC CPUs over time have added complex instructions such as hardware multiply/divide which had to be done purely in software in early RISC designs. Additionally, instruction set extensions like the Visual Instruction Set (VIS) on UltraSPARC or AltiVec on PowerPC allow for DSP-like (SIMD) functionality just like MMX/SSE do on x86.

So what is a modern x86 CPU then ? CISC or RISC ?

The answer is:

Both. It is a CISC CPU, but to perform best, one has to program it like a RISC CPU.

For example, AMD in their Software Optimization Guide for AMD Athlon64 and AMD Opteron Processors explains it like this:

The AMD64 instruction set is complex; instructions have variable-length encodings and many perform multiple primitive operations. AMD Athlon 64 and AMD Opteron processors do not execute these complex instructions directly, but, instead, decode them internally into simpler fixed-length instructions called **macro-ops**. Processor schedulers subsequently break down macro-ops into sequences of even simpler instructions called **microops**, each of which specifies a single primitive operation. and a little later:

Instructions are classified according to how they are decoded by the processor. There are three types of instructions:

#### Instruction Type Description

| DirectPath Single | A relatively common instruction that the processor   |

|-------------------|------------------------------------------------------|

|                   | decodes directly into one macro-op in hardware.      |

| DirectPath Double | A relatively common instruction that the processor   |

|                   | decodes directly into two macroops in hardware.      |

| VectorPath        | A sophisticated or less common instruction that the  |

|                   | processor decodes into one or more [ ] macro-ops [ ] |

|                   |                                                      |

and finally:

.

Use DirectPath instructions rather than VectorPath instructions.

In short:

Bypass the CISC runtime translation layer to get best performance out of the underlaying RISC execution engine.

Similar notes can be found in the respective manuals for Intel's Pentium IV CPU family and later.

## 2.2.2.Endianness

The x86 CPU family is traditionally *Little Endian*. What does this mean ?

The topic of how bytes that form multi-byte (or, for that matter, multi-bit) entities should be ordered in the past used to have almost religious traits. This is the reason why the technical term for memory byte ordering, *Endianness*, was taken from *Gulliver's Travels* by Jonathan Swift and refers to the holy war between the two empires of Lilliput and Blefuscu about the question which *end* eggs are to be opened at first.

Illustration 4 - On the origin of the term "Endianness"

The original reference which coined the term seems to be a posting by David Conen in his famous essay "*On holy wars and a plea for peace*", which dates from the 1st of April 1980 and became a classic on that subject after it was published by the IEEE computing magazine in 1981. The article is also known under the reference number IEN-137.

| Data ordering in little endian mode  | Data ordering in big endian mode     |

|--------------------------------------|--------------------------------------|

| utsname+0x303?s                      | utsname+0x303?s                      |

| utsname+0x303: snv_24                | utsname+0x303: snv_24                |

| > utsname+303?J                      | > utsname+0x303?J                    |

| utsname+0x303: 736e765f32340000      | utsname+0x303: 736e765f32340000      |

| > utsname+303?2X                     | > utsname+0x303?XX                   |

| utsname+0x303: 32340000 736e765f     | utsname+0x303: 736e765f 32340000     |

| > utsname+303?4x                     | > utsname+0x303?4x                   |

| utsname+0x303: 0 3234 765f 736e      | utsname+0x303: 736e 765f 3234 0      |

| > utsname+303?8B                     | > utsname+0x303?8B                   |

| utsname+0x303: 0 0 34 32 5f 76 6e 73 | utsname+0x303: 73 6e 76 5f 32 34 0 0 |

When a processor accesses a multi-byte data type (i.e. C types **short**, **int**, **long**, **long long**) from memory in a single operation, it will make an implicit assumption what comes first – the *most significant byte* (MSB) or the *least significant byte* (LSB). These terms are used interchangeably with Endianness,

• LSB (least significant byte first) : Little Endian

• MSB (most significant byte first) : Big Endian

As there is endianness on byte level, there's also endianness on bit level, i.e. regarding the ordering of bits within a byte. But this poses less problems than byte ordering, because apart from serial protocols little data exchange is done on bit-level, and fortunately mixed-endian CPUs that used little endian for bits and big endian for bytes or vice versa (yuck – like ancient greek written in a mode called " $\beta_{0000T}\rho_{000}\delta_{00}v$ ", "like the ox plows" - one line from left-to-right, and the next right-to-left) are no longer on the market. Today, big-endian CPUs use big endian for both bit and byte ordering, and likewise little-endian CPUs.

To a CPU, reading numbers from memory, aka ordering bytes within a word, is like reading a text to humans – words are made up from characters, and you read them from left-to-right – unless, of course, you're reading Arabic or Hebrew texts, or traditional chinese, where you read them from right-to-left. There is no inherent advantage or disadvantage to do it either way, and what's supposed to be the correct way of doing it depends on the CPU/language you use. But a consequence is that what feels natural to one seems very odd to the other.

So accessing data the big-endian way is like reading left-to-right, while little-endian is like reading right-to-left and therefore may look odd. But if the output is formatted, it becomes clear again:

| Little Endian: Right-aligned pointers |                  | Big Endian: Left-aligned pointers |  |

|---------------------------------------|------------------|-----------------------------------|--|

| utsname+101/J                         |                  | utsname+101/J                     |  |

| utsname+0x101:                        | 6361626863746168 | utsname+0x101: 6361626863746168   |  |

| <pre>&gt; utsname+101/X</pre>         |                  | <pre>&gt; utsname+101/X</pre>     |  |

| utsname+0x101:                        | 63746168         | utsname+0x101: 63616268           |  |

| <pre>&gt; utsname+101/x</pre>         |                  | <pre>&gt; utsname+101/x</pre>     |  |

| utsname+0x101:                        | 6168             | utsname+0x101: 6361               |  |

| <pre>&gt; utsname+101/B</pre>         |                  | <pre>&gt; utsname+101/B</pre>     |  |

| utsname+0x101:                        | 68               | utsname+0x101: 63                 |  |

The difference in endianness between e.g. x86 (little endian) and SPARC (big endian) becomes relevant as soon as data is exchanged between two machines of differing endianness. Even within the same system this can happen, in the case the CPU and a peripheral device use different endianness but share memory. Whenever file contents, shared memory or network packets are exchanged between two parties that use different endianness, a common storage format must be agreed on, or a method to swap endianness must be found.

Examples how to deal with endianness are:

#### Network Byte Ordering.

On creating network packet contents, the sender is supposed to use the host-tonetwork interfaces, **htonl()** etc., to convert data to the network byte ordering, while the receiver shall use the corresponding network-to-host functions, **ntohl()** etc., to decode network data into its native format.

Network byte ordering is big-endian, but it is unportable to program based on that assumption. It's also unnecessary – on big-endian machines, the interfaces for host/network byteorder conversion will do nothing – they'll simply pass through their input. Compiler optimizers eliminate these calls on big-endian systems.

#### See manpage byteorder(3SOCKET).

Remote Procedure Calls (RPC).

Passing RPC arguments between two systems requires an endian-agnostic data representation. This is called XDR (exchangeable data representation), and a

library is supplied that programs can use to convert a huge variety of basic data types into XDR representation. XDR is a generalization of network byte ordering to arbitrary data types. See manpage xdr(3NSL).

#### DMA Memory Access by device drivers.

Peripheral devices and the main CPU in a machine may access memory with differing endianness. When writing a device driver for such a device, the programmer therefore needs an interface to specify to the host operating system that a given device is big- or little-endian. Depending on whether device and host use the same or a different byte ordering, data to be transferred to or from that device must be converted into the proper byte order. Under Solaris, the DDI interface set provides routines to request byte swapping to be done by the framework. See manpages:

ddi\_device\_acc\_attr(9S), ddi\_dma\_mem\_alloc(9S) and ddi\_dma\_sync(9S).

## 2.3.Marketeering – Naming the architecture

Illustration 5 - Pieter Brügel, Tower of Babel

The number of trademarked and non-trademarked terms applied to "x86 CPUs" and software that runs on the "x86 platform" is legend, and marketing departments everywhere keep adding to it.

Naming the architecture is truly the Babel of the computing industry.

- The term "x86" and derivatives of that is generic (not trademarked), and commonly used to describe all architectures (by various vendors) that were in one way or the other "derived" from the original Intel 8086 microprocessor, and have a high degree of compatibility with Intel CPUs.

- The same applies to "PC compatible" though that includes more than just a CPU that is "x86 compatible". The original IBM PC/AT (trademarked terms, again) had, in addition to the i8086 CPU, a set of standard hardware/peripherals whose presence can be assumed on "compatibles". Later, Microsoft, Intel and other hardware vendors devised updated "PC XX" standards to list a set of hardware/bus interfaces available by default on "modern" systems.

- Intel uses the trademarked terms "Intel Architecture", and more specifically "32bit Intel Architecture" (IA32). Intel always had more than one CPU architecture in their portfolio (e.g. today the Itanium/IA64, in the past the i860 RISC, even before that the i437) so "Intel Architecture" alone doesn't mean anything technically. IA32, on the other hand, is the term applied to the instruction set/feature set of Intel CPUs whose ancestor is the 8086 in short, IA32 is "x86 by Intel".

- The CPU names i8086, i80286, i80386, i80486, Pentium, ... are Intel trademarks.

- UNIX platforms have traditionally shortened these to i86, i286, i386 (with and without the leading 'i'). "386" is particularly frequent as the first 32bit version. "386" and variants thereof is found all over:

\$ file ls

```

ls: ELF 32-bit LSB executable 80386 Version 1,

dynamically linked, stripped

```

```

$ uname -a

SunOS hatchback 5.10.1 onnv-work i86pc i386 i86pc

$ isainfo

amd64 i386

We also find it, for example, in the ELF format architecture name:

<sys/elf.h>: #define EM 386

3

/* Intel 80386 */

It's also present as the conditional-compile definition for 32bit x86:

<sys/isa defs.h>:

[ ... ]

/*

* The feature test macro ____i386 is generic for all processors implementing

* the Intel 386 instruction set or a superset of it. Specifically, this

* includes all members of the 386, 486, and Pentium family of processors.

*/

#elif defined(__i386) || defined(i386)

/*

* Make sure that the ANSI-C "politically correct" symbol is defined.

*/

#if !defined( i386)

#define i386

#endif

[...]

Intel itself never used the terms "i586", "i686" (with or without the 'i') or similar,

```

but other CPU vendors (like AMD or Cyrix) did, and e.g. the GNU gcc compiler recognizes **-m586** and similar as hint to optimize code for post-486 processors.

The confusion about names doesn't get better with the extension to 64bit.

The 64bit extension was created and first specified by AMD. AMD called this "x86\_64" during development (and the term is still used as the architecture name on Linux), and "AMD64" on release.

In fact, both are found as the ELF architecture name:

<sys/elf.h>:

| #define EM_AMD64  | 62       | /* AMDs x86-64 architecture */ |

|-------------------|----------|--------------------------------|

| #define EM_X86_64 | EM_AMD64 | /* (compatibility) */          |

AMD64 applies to the instruction set (x86 including 64bit extensions).

- The AMD Opteron and Athlon64 are CPUs by AMD implementing the AMD64 architecture.

- Intel for obvious reasons does *not* use the term "AMD64". Since "IA64" is already given to the (x86-incompatible) Itanium architecture, Intel has created two new names of its own instead:

- EM64T (Extended Memory 64bit technology)

- IA32e

The first is applied to processors by Intel that are "AMD64 compatible", while the second (which is very uncommon) is used in Intel's architecture reference manual to describe the 64bit x86 instruction set (extension).

• Microsoft and Sun, for example, chose to use the term "x64" when talking about the 64bit x86 architecture, resp. their operating systems supporting it. In that context, "x86" means 32bit-x86, while "x64" means 64bit-x86.

In this document, the term "x86" is used wherever possible, with a specific note "32bit", "32bit mode", "64bit" etc. as appropriate.

## **3.Assembly Language on x86** platforms

From "The Tao of Programming":

The Tao gave birth to machine language. Machine language gave birth to the assembler.

The assembler gave birth to the compiler. Now there are ten thousand languages.

## **3.1.Generic Introduction to Assembly language**

Programming languages, however they are structured, tend to implement a common set of minimum functionality. Programming languages usually have features like:

- *instructions*, i.e. operations to modify and query "state"

- "state" (operands/variables/data) that instructions operate on

- modularization (the ability to substructure both program and data into smaller reusable units of execution/access, termed *functions/structures*)

Assembly language of course supplies all of these. The purpose of this section is to explain how constructs used in x86 assembly language implement these basic building blocks. Since this manual is not supposed to replace introductory tutorials on either programming in general nor machine-level programming as such, no attempt will be made to explain things like "what is an instruction", "what is an expression". Minimum familiarity with programming is assumed.

To understand assembly language programs (or disassembled compiled code), look at the above list of language building blocks again in more detail.

### 3.1.1.Instructions

Assembly language uses *mnemonics* (human-readable transcript of the actual binary machine code) for instructions. The following classes are usually supplied:

- 1. arithmetic/logical instructions. Anything that actually modifies data (aka performs an operation) falls under this category. Examples are addition, multiplication, and other numerical operations.

- 2. comparisons and conditionals to query state and change the flow of execution depending on that state. A typical example would be a "check if lower than" or a "branch if equal" instruction.

- 3. Load/Store operations for data transfer

- 4. function subroutine support, aka call/ret instructions (instruction transfer)

How readable the assembly language for a specific processor is depends somewhat on the choice of the CPU vendor how to name the instructions.

Intel for the x86 CPU family has used plain english terms (or at worst simple abbreviations) for assembly instruction names. A typical example would be the name of the instruction that calculates the sum of two operands: "**ADD**". At worst, an abbreviation as "**MOVNTQA**" (Move non-temporal quadword aligned) can occur, but in most cases x86 assembly instruction names are descriptive.

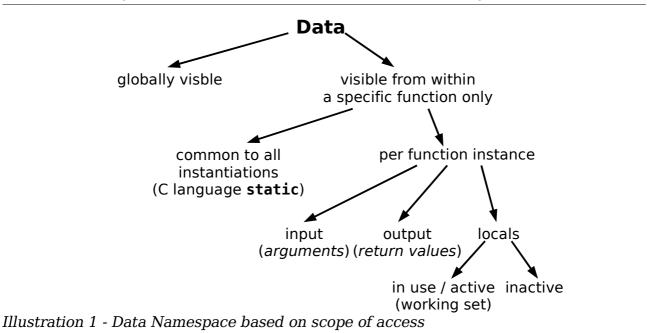

## 3.1.2. Operands, Variables and Data

To understand the concepts used in assembly language for accessing data, we have to examine more closely what data can be. More precisely, what the *scope* (visibility) of a particular item is.

One possible way how data can be classified in a hierarchical way would be:

This is not the only possible subclassification of "data", of course, but the above scheme has the advantage that it maps very well to some of the concepts inherent to assembly language.

From the point of view of currently executing machine code, data can be considered to be "closer" and "further" away.

- Data that can be seen from any code within the current program is called *global*. Global data is persistent, it will continue to exist even if the specific piece of code that happened to be using it has been completed.

- The C programming language knows a specific subtype of global data that is called **static**. Static data in C is not visible to every code from the current program but only to code from the same sourcefile, or to all instantiations (calls) of a given function. C static also is persistent.

- Any other data in use by the program is temporary and only lives as long as the current function is executing. Such data is recreated/reinitialized each time a given function is run, and different functions operate on different sets of data. This is generically called *local data*. It is usually subclassed further into:

- Function input: *Arguments*

- Function output: *return value(s)*

- Other non-persistent data in use by the function: *local variables*

- Structured programming languages have finer-grained blocks of execution than functions. Consider, for example, a loop within a function. It uses data, though in most cases not all of the data that this function is operating on. Instead, it uses only a subset of that. This subset of currently-in-use data is called the *working set*. For optimal performance, a method is desired to access data from the working set in

as fast a way as possible.

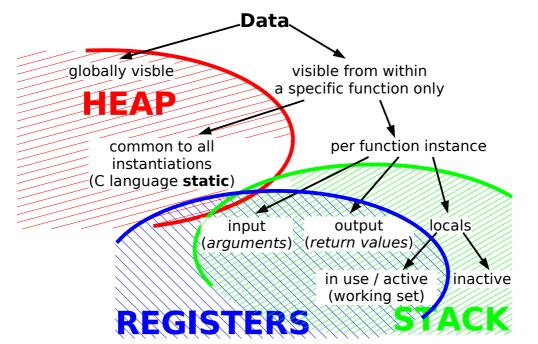

Illustration 2 - Machine-Language concepts for heap, stack and registers

In terms of machine-level architecture, data as classified above therefore falls into three big groups:

- 1. Global, persistent data. This is the *Heap*.

- 2. Temporary data which lives as long as the function that uses it is executing. This is usually called the *Stack*.

- 3. Data that makes up the current working set. Most CPUs provide fast-access temporary storage for such data a set of *Registers*.

## 3.1.3. Registers, the Stack and the Heap

A high-level programming language often does not inherently know the concept of *memory*. Where data is stored or how it is accessed is up to the internal implementation of the language and not usually exposed to the programmer. Even intermediate-level languages like "C" that supply language features for specifying *data locality* (C keywords **extern/static/auto/register**, pointers) don't usually specify how these features are implemented, but refer to "the architecture" to supply the backend. Assembly language is different here. Due to the tight binding between hardware features and assembly language, the programmer here has to know about the details regarding where data is stored, resp. consider the optimal place where to put operands at any given time. This is where the above diagram comes in handy.

Assembly language at least knows the distinction between *persistent* and *temporary* data – the *heap* and the *stack*. There are machines out there (the Java Virtual Machine, or Forth, for example) which implement nothing else, but most current processors provide hardware support for putting a *working set* of data into fast temporary storage – a set of *registers*.

CPU Registers are kind of a "Level 0 Cache" (and the existance of registers as a fastaccess temporary data storage far preceeds the existance of CPU caches) within the CPU, and used to hold variables that are either frequently queried or being modified as part of a computation. In many CPUs, arithmetic operations require the presence of the operands within registers. CPU registers, provided enough of them are available, will be the place where the *working set* of variables for the current function is found.

But even modern CPUs created/designed at a time when space on the CPU die is aplenty, don't offer unlimited number of registers. On the contrary, registers are usually a scarce resource. This is where the *stack* comes in again - to serve as a backing store for local variables. By giving each function its own dedicated piece of memory specific to this instantiation (i.e. different for e.g. two CPUs calling the same code), a so-called *stack frame*, the function can "swap" its working set between stack (or heap) and registers.

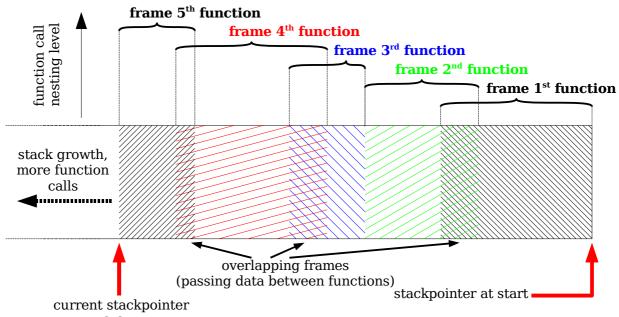

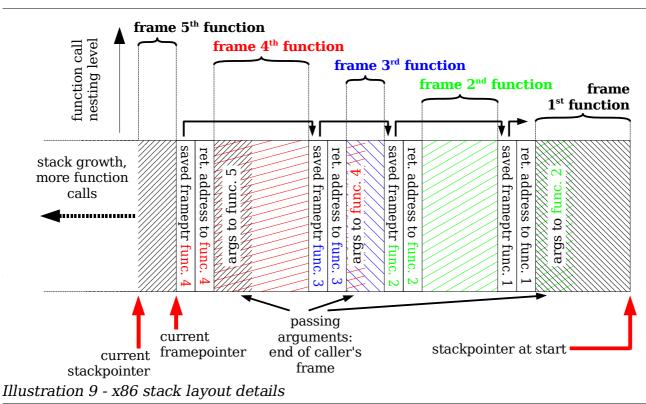

Registers and/or the stack frame also serve for data-passing between nested function calls. By letting the frames of calling and called function overlap, arguments can be passed between functions or values returned.

Data that is not specific to one instantiation of a function call but shared between all calls to this function (a C **static**), or all calls to all functions (a global variable) will not end up in the stack but in a well-defined location in memory that every code knows about. This memory location is often called the *data segment* of the program, or the *heap*.

## 3.2.Assembly language on x86 platforms

## 3.2.1.Registers

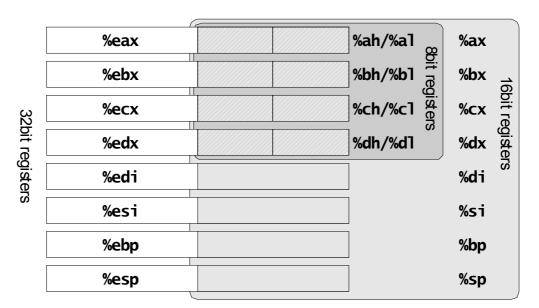

The general-purpose x86 register set has evolved from the 8bit i8008 processor's AH/AL accumulator model via the eight 16bit registers of the i8086 processor, and their extension (hence the register name prefix 'E') to 32bit in the i80386 and 64bit in the AMD Opteron. All registers are global, and 16/8bit register names are only alias names for lower bits of the 32bit register. This is called *register aliasing*. In 32bit mode, x86 processors implement the following general-purpose registers:

Illustration 3 - Register set (integer registers) on x86 architectures in 32bit mode

Overall, x86 CPUs in 32bit mode have only eight global, general-purpose registers. They are shared between 32/16/8bit access:

- 32bit registers : EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP

- 16bit registers : **AX**, **BX**, **CX**, **DX**, **SI**, **DI**, **BP**, **SP** These registers cover bit 0..15 of the corresponding 32bit registers.

- 8bit registers : AL, BL, CL, DL, and AH, BH, CH, DH, These registers cover bits 0...7 (.L) or bits 8..15 (.H) of registers EAX ... EDX.

Processors in the x86 family supply many more registers than that, but none of these are general-purpose. Instead, specific instructions are required to make use of those. Commonly-seen special registers in x86 include:

- The processor state register(s): **EFLAGS**, **CR0**...**CR8**.

- The program counter (instruction pointer) register: **EIP**.

- Floating point and vector registers: ST0..ST8, MM0..MM8, XMM0..XMM8

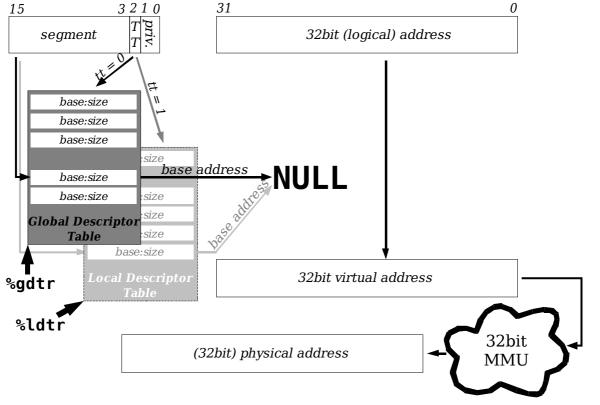

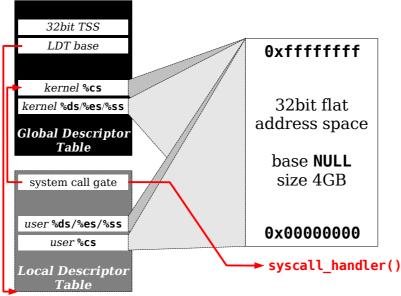

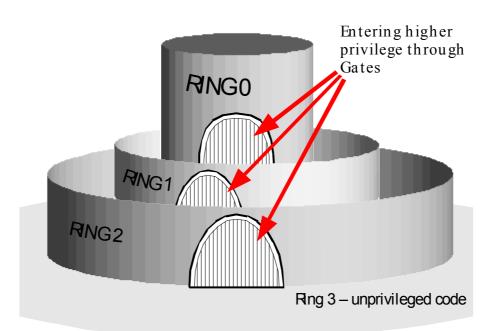

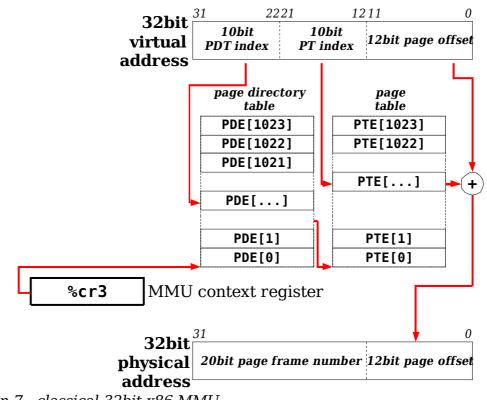

Peculiar to the architecture is the concept of segmentation, which also is controlled via a special set of registers:

- Descriptor Table registers: **GDTR**, **LDTR**, **IDTR**

- Segment registers: CS, DS, ES, FS, GS, SS

Modern x86 CPUs supply hundreds of registers, all of them special-purpose. They are

called *machine-specific registers*, or MSR, and control specific features of the given CPU. Please refer to the processor manuals from the respective CPU vendors.

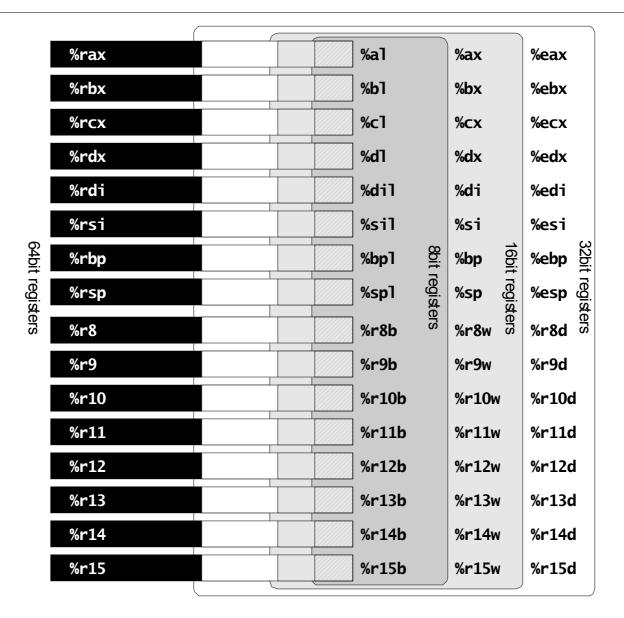

In 64bit mode (AMD64 and EM64T processors), the general-purpose register set is twice as large as before, and access to 16/8bit "subregisters" has been unified:

Illustration 4 - Register set (integer registers) on x86 architectures in 64bit mode

64bit mode retains register aliasing but makes it uniform. In addition to that, the number of general-purpose registers (and the number of XMM vector registers) has been doubled. In 64bit mode, the CPU provides:

- 16 64bit registers : RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP and R8..R15.

- 16 32bit registers : EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP and R8D..R15D. These registers map bits 0..31 of the corresponding 64bit register.

- 16 16bit registers : AX, BX, CX, DX, DI, SI, BP, SP and R8W..R15W. These registers map bits 0..15 of the corresponding 32/64bit register.

- 16 8bit registers : AL, BL, CL, DL, DIL, SIL, BPL, SPL and R8B..R15B.

These registers map bits 0..7 of the corresponding 16/32/64bit register.

In 64bit mode, the "highbyte" registers **AH**..**DH** are deprecated; they still are available but their use is no longer suggested for 64bit code.

The 64bit x86 register set is uniform – all registers can be used in the same way, i.e. all of them have 8/16/32bit "subregisters". That doesn't mean all of them are equally efficient, though. The x86 instruction set has "optimized machine opcodes" for some arithmetic operations that put their result into **%eax/%rax**, for example. Likewise, the 64bit extensions encode the use of **%r8**..**%r15** via an additional byte in the instruction stream, so the use of the "classical" registers vs. the "new" registers creates more compact binary code. Please refer to the CPU vendors' optimization guidelines for instructions on how to optimally use the register set if you intend to write assembly code for 64bit x86 platforms manually.

64bit mode also has the **FLAGS** register (**RFLAGS**), and the 64bit program counter **RIP**, which is made explicitly available for PC-relative addressing, a feature not available in 32bit code.

Register aliasing requires rules that specify how the high bits of the 16/32/64bit register are handled if an instruction operates explicitly on a 32/16/8bit register:

- A 8bit operation on .L does not affect bits 8..31 (i.e. the upper bits in the .X and E.. registers). Operating on .H, bits 0..7 and 16..31 are unaffected.

Bits 32...63 of the 64bit R.. register are cleared.

- A 16bit operation does not affect bits 16..31 (i.e. the upper bits in E../R..D). Bits 32...63 of the 64bit R.. register are cleared.

- A 32bit operation clears bits 32..63 of the 64bit R... register.

In other words, if operating in 64bit mode, all operations that are not explicitly 64bit will zero extend their result to 64bit. The advantage of doing this is in preserving the semantics of all existing 32bit operations. For example, a 32bit addition will overflow after 32bit and set status register bits to indicate this condition, instead of silently wrapping around to 64bit and preventing proper detection of the 32bit overflow.

## 3.2.2.Addressing Modes

Accessing memory is possible either:

- *Direct,* supplying an absolute 32/64bit value as address

- *Register indirect*, using the value contained in a register as address

- *Indirect with offset,* using the contents of a register as the base address and a (no larger than 32bit) constant as additional offset

- *Indirect with index and scale,* using a register as base address of an array, a second register as index into that array and a scale factor of 1, 2, 4 or 8 for that register to specify the size of the elements in the array.

- *Indirect with offset, index and scale*. Same as before, except that now the start address of the array will be the sum of base register and offset. This allows e.g. to efficiently access arrays that are themselves members of larger data structures.

- *instruction pointer relative with offset*. This is only available in 64bit mode and allows for efficient position-independent code.

As a summary, memory access on x86 systems is done by calculating the address implicitly using the following formula:

| memory location = <b>offset</b> +   | %rax<br>%rbx<br>%rcx<br>%rds<br>%rsi<br>%rdi<br>%rbp<br>%rsp<br>%r8<br><br>%r15 | $+ \begin{pmatrix} 1 \\ 2 \\ 4 \\ 8 \end{pmatrix} \times$ | % rax<br>% rbx<br>% rcx<br>% rdx<br>% rsi<br>% rdi<br>% rbp<br>% rsp<br>% r8<br><br>% r15 |  |

|-------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| tion-pointer-relative (64bit only): |                                                                                 |                                                           |                                                                                           |  |

instruction-pointer-relative (64bit only):

memory location = **offset** + **%rip**

Illustration 5 - Summary of x86 addressing modes

Any parts are optional. In 32bit mode, only the 32bit registers **%eax...%esp** can be used, of course.

The stack is special on x86, and the architecture has explicit support for accessing stack memory – via PUSH/POP instructions.

*Pushing something onto the stack* will decrement **%esp/%rsp** by the size of the operand and put the value of the operand into the memory location that **%esp/%rsp** points at then.

*Popping something off the stack* takes the value the **%esp/%rsp** points at, and then increments **%esp/%rsp** by the size of the operand.

## 3.2.3.x86 assembly syntax

On most processors, the assembly language (i.e. the human-readable mnemonics) has been created by the CPU vendor. This of course also applies to x86, but the story doesn't end there. On x86 systems, there are *two dialects* of assembly language:

- Intel Syntax

- AT&T Syntax

For non-UNIX assembly programmers, Intel's official assembly language syntax will be used. But on UNIX systems, the situation is traditionally reversed. After Intel released the 80386 processor with its 32bit capabilities, AT&T's UNIX System Laboratories were one of the first operating system vendors to create a 32bit operating system for it. Since there was no existing 32bit-x86 market in 1985, there were also no readily-available development toolchains (compiler, assembler, linker) for them to use, so this had to be written, in the case of the assembler from scratch. Legend has it that AT&T developers looked at Intel's assembly language specification and were horrified by the ambiguities in the syntax, and the strong dissimilarity of Intel's assembly language syntax to those of other CPUs that UNIX had been ported to before.

So AT&T devised their own assembly language syntax for x86 platforms, which is standard for x86 assembly on UNIX and UNIX-like systems.

On binary level, there's of course only one x86 machine language. AT&T and Intel Syntax are just a different way of making the machine language human-readable. As an analogy, consider writing the same chinese-language text with chinese characters and in the pinyin style using latin characters – striking differences, but yet it's chinese. Fortunately, the differences between AT&T syntax and Intel syntax are smaller than that.

| Operation                                        | AT&                                          | Г Syntax                                                                                                                | Inte                                   | l Syntax                                                                                                                                           |

|--------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Move data from<br>memory into a<br>register      | movb<br>movw<br>movl<br>movq                 | address, %ah<br>address, %ax<br>address, %eax<br>address, %rax                                                          | MOV<br>MOV<br>MOV<br>MOV               | AH, [ address ]<br>AX, [ address ]<br>EAX, [ address ]<br>RAX, [ address ]                                                                         |

| More Addressing:<br>Direct, Indirect,<br>Indexed | movl<br>movb<br>movq<br>movl<br>movw<br>movw | address, %edi<br>-0x20(%ebp), %dl<br>(%rax,%rcx), %r12<br>(%edx,%esi,4), %edx<br>0x8(%ebp,%ecx), %si<br>\$0, 0x20(%ebx) | MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV | EDI, [ address ]<br>DL, [ EBP - 0x20 ]<br>R12, [ RAX + RCX ]<br>EDX, [ EDX + 4 * ESI ]<br>SI, [ EBP + ECX + 0x8 ]<br>WORD PTR<br>[ EBX + 0x20 ], 0 |

|                                                  | movl                                         | %r12d, 12345(%rip)                                                                                                      | MOV                                    | [ RIP + 12345 ], R12D                                                                                                                              |

| Use of constants                                 | addb<br>subl                                 | \$10, %r15b<br>\$1234, -0x10(%rbp)                                                                                      |                                        | R15B, 10<br>INT PTR<br>[ RBP - 0x10 ], 1234                                                                                                        |

|                                                  | orl<br>xorl<br>movq<br>andl                  | \$0x10110, %ebx<br>\$0xffffffff, %ecx<br>\$0x123456789abcdef0, %rax<br>\$0xfffffff0, %esp                               | OR<br>XOR<br>MOV<br>AND                | EBX, 0x10110<br>ECX, 0xffffffff<br>RAX, 0x123456789abcdef0<br>ESP, 0xfffffff0                                                                      |

| Arithmetics                                      | xorl<br>addl<br>andl<br>andl                 | %eax, %eax<br>%ecx, %edx<br>\$0x1000, %esi<br>\$0x10, -0x30(%ebp)                                                       | XOR<br>ADD<br>AND<br>AND               | EAX, EAX<br>EDX, ECX<br>ESI, 0x1000<br>INT PTR<br>[ EBP — 0x30 ], 0x10                                                                             |

Some simple examples illustrate differences between Intel and AT&T syntax very well:

| Operation               | AT&T Syntax                                                           | Intel Syntax                                         |  |

|-------------------------|-----------------------------------------------------------------------|------------------------------------------------------|--|

|                         | imulq %rax, %rbx, %rcx<br>orl \$0x400, %r13d<br>addb \$123, globalvar | IMUL RCX, RAX, RBX<br>OR R13D, 0x400<br>ADD BYTE PTR |  |

|                         | leal (%eax,%eax,4), %eax                                              | [ globalvar ], 123<br>LEA EAX, [ EAX + 4 * EAX ]     |  |

|                         | leal (%eax,%ebx), %ecx                                                | LEA ECX, [ EAX + EBX ]                               |  |

| Control transfer        | call funcX<br>call *%ebx<br>ret<br>iret                               | CALL func<br>CALL [EBX]<br>RET<br>RET FAR            |  |

|                         | lcall \$0x27,0<br>jae func+0x123                                      | CALL FAR 0, 0x27<br>JAE func+0x123                   |  |

| Special<br>Instructions | cmpxchgl %eax, (%ecx)<br>cmpxchgq %rdx, (%r15)                        | CMPXCHG [ ECX ], EAX<br>CMPXCHG8B [ R15 ], RDX       |  |

|                         | repz<br>scasb                                                         | REPZ CASB                                            |  |

|                         | pushal<br>movl %xmm5, (%eax,%ebx)                                     | PUSHAD<br>MOVD [ EAX + EBX ], XMM5                   |  |

|                         | lock<br>orl \$0x800,(%rax)                                            | LOCK OR INT PTR<br>[ RAX ], 0x800                    |  |

In general, AT&T syntax has been designed to remove ambiguities that are inherent to Intel syntax. The differences can be summed up as follows:

- AT&T prefixes register names with '%' to avoid ambiguities with names of variables. Intel reserves the names of registers. If a variable uses a name that the next Intel CPU uses for a register – you're out of luck.

- AT&T prefixes constants (whether numerical values or symbols whose address is to be taken as a constant) with '\$'. Intel does not specifically mark constants. Again, ambiguities between register names and variable names possible.

- AT&T orders operands source first, destination second, i.e. a from-to ordering. Intel uses destination first, source second. Operations are "do to <>: .".<>

- AT&T suffixes instruction names with **b**, **w**, **l** or **q** to specify the operand size. Intel derives the operand size implicitly from the name of the target register. In cases where the target is memory, the ... **PTR** syntax extension is used.

- AT&T uses a format offset(%base,%index,scale) for address declarations. Intel puts the formula in square brackets, [ BASE + SCALE \* INDEX + OFFSET ]

- AT&T in assembly sourcecode (not in disassembler output, though) puts instruction prefixes onto separate lines. Intel requires instruction prefixes to directly preceed the instruction they apply to.

- AT&T and Intel name a small set of instructions differently, in cases where the size suffix in AT&T syntax makes a new instruction name unnecessary, for string instructions, or far calls/returns.

- AT&T by convention uses lowercase, and variable names are case-sensitive. Intel syntax uses capital letters for everything.

Keep the differences between AT&T and Intel syntax in mind if you're reading Intel's or AMD's architecture reference manuals – these all use Intel syntax. Especially the

different argument ordering can be confusing at times.

For porting assembly sourcecode written in Intel syntax to AT&T syntax, the "shortcut" via assembling it using an Intel-syntax-aware assembler, and disassembling it with one that outputs AT&T assembly is suggested.

As far as this document is concerned, AT&T syntax will be used. This is the x86 assembly language found in the Solaris sourcecode, and the kind of disassembler output one gets when using debugging tools on the Solaris operating system.

# 3.3.x86 assembly on UNIX systems – calling conventions, ABI

The x86 architecture supplies instructions for stack- and framepointer maintenance and **call/ret** instructions for performing function calls. But this is not sufficient. From architectural constraints, no rules exist for:

- how does the caller *pass arguments* to the called function ?

- how does the called function *return results* to the caller ?

- What happens with contents of the (global) registers when doing a **call** ?

In addition to that, x86 in hardware only knows basic C data types **char**, **short**, **int**, **(long) long**, **float** and **double**. What about compound data types – arrays and structures ? How are these laid out in memory ?

Compiled code should better agree on a common set of rules for passing arguments and returning values, for register usage and data structure layout, or else linking code from a library and a user-supplied program together is going to break big-time. This is why operating systems define *standard calling conventions* which all dynamicallylinked code on this platform must obey. This is called the *Application Binary Interface*, or short ABI.

The ABI usually is a big document that defines much more than just the standard calling conventions for binary code. Details on functions in the standard libraries, software packaging and installation rules or lists of software programs that are considered an essential part of the system are also in the ABI.

For UNIX systems derived from AT&T UNIX System V R4, like Solaris, the relevant document is the System V ABI. It contains:

- A generic (platform-independent) part listing things common to all platforms UNIX has been ported to

- A *platform supplement* part, chapter 3, that details the abovementioned platformspecific calling conventions and data layout rules for a specific architecture. When one talks about "the i386 UNIX ABI" or "the x86-64 UNIX ABI", what's meant is the platform-specific chapter 3 ABI supplement for the given architecture.

To illustrate the calling conventions on x86 systems, we'll investigate compilergenerated assembly code for a simple C language program:

```

#include <strings.h>

```

```

* A compound data structure consisting of several primitive types

*/

typedef struct {

char s_c;

unsigned short s_us;

long s_l;

int s_i;

char s_name[256];

struc_t *s_next;

} struc_t;

* C "constructor" for struc_t

*/

int init_struc(

struc_t *s,

char i_c,

unsigned short i_us,

int i i,

long i_l,

char *i name,

struc_t *i_next)

{

s->s_c = i_c;

s \rightarrow s_u s = i_u s;

s \rightarrow s_i = i_i;

s - s = i ;

s->s next = i next;

strncpy(s->s_name,

i name,

sizeof(s->s_name));

return (1);

```

}

It depends on compiler and optimization how the assembly will look like in the end; the code below was created using the Sun Workshop compiler, version 10, on a system running Solaris 10. The ABI is different for 32bit and 64bit binaries, as will be shown.

## 3.3.1.The i386 UNIX ABI – 32bit x86

First, the 32bit assembly code created from the above:

| function offset            | binary opcode     | assembly                          | C sourcecode                    |

|----------------------------|-------------------|-----------------------------------|---------------------------------|

| init_struc                 | 55                | pushl %ebp                        | <pre> init_struct(</pre>        |

| init_struc+0x1             | 8b ec             | movl %esp,%ebp                    | –                               |

| init_struc+0x3             | 83 e4 f0          | andl <pre>\$0xfffffff0,%esp</pre> | ) {                             |

| init_struc+0x6             | 8a 45 0c          | <pre>movb 0xc(%ebp),%al</pre>     |                                 |

| init_struc+0x9             | 8b 4d 08          | <pre>movl 0x8(%ebp),%ecx</pre>    |                                 |

| init_struc+0xc             | 88 01             | <pre>movb %al,(%ecx)</pre>        | s->s_c = i_c;                   |

| init_struc+0xe             | 66 8b 45 10       | movw 0x10(%ebp),%ax               |                                 |

| init_struc+0x12            | 66 89 41 02       | <pre>movw %ax,0x2(%ecx)</pre>     | s->s_us = i_us;                 |

| init_struc+0x16            | 8b 45 14          | <pre>movl 0x14(%ebp),%eax</pre>   |                                 |

| init_struc+0x19            | 89 41 08          | <pre>movl %eax,0x8(%ecx)</pre>    | s->s_i = i_i;                   |

| init_struc+0x1c            | 8b 45 18          | <pre>movl 0x18(%ebp),%eax</pre>   |                                 |

| init_struc+0x1f            | 89 41 04          | <pre>movl %eax,0x4(%ecx)</pre>    | s->s_l = i_l;                   |

| init_struc+0x22            | 8b 45 20          | <pre>movl 0x20(%ebp),%eax</pre>   |                                 |

| <pre>init_struc+0x25</pre> | 89 81 0c 01 00 00 | <pre>movl %eax,0x10c(%ecx)</pre>  | s->s_next = i_next;             |

| init_struc+0x2b            | 68 00 01 00 00    | pushl \$0x100                     | <pre>sizeof(s-&gt;s_name)</pre> |

| init_struc+0x30            | ff 75 1c          | pushl 0x1c(%ebp)                  | i_name                          |

| init_struc+0x33            | 83 cl 0c          | addl \$0xc,%ecx                   | &s->s_name                      |

| init_struc+0x36            | 51                | pushl %ecx                        | _                               |

| init_struc+0x37            | e8 fc ff ff ff    | call <strncpy></strncpy>          | <pre>strncpy();</pre>           |

| init_struc+0x3c            | b8 01 00 00 00    | movl \$0x1,%eax                   | return (1);                     |

| init_struc+0x41            | 8b e5             | movl %ebp,%esp                    |                                 |

| init_struc+0x43            | 5d                | popl %ebp                         |                                 |

| init_struc+0x44            | c3                | ret                               | }                               |

The disassembler output is color-coded in the table above to highlight specific areas:

- Green shows function prologue and function epilogue.

- **Red** shows how **init\_struc()** accesses its own arguments.

- **Blue** shows access to different members of **struc\_t**.

This simple example therefore suffices to demonstrate the rules in the i386 UNIX ABI supplement.

How are arguments passed to a function ? Where does a function find its own arguments ?

Look at the call to **strncpy()**. Its arguments are **pushl**'ed to the stack, in reverse order, i.e. argN pushed first, arg0 last – immediately before the **call**.

Likewise, look at the way **init\_struc()** accesses its own arguments. This is the code marked *red*. Its arguments are found at:

| +0x8(%ebp) struc_t *s |                     | argument 1 |

|-----------------------|---------------------|------------|

| +0xc(%ebp) char       | i_c                 | argument 2 |

| +0x10(%ebp)           | unsigned short i_us | argument 3 |

| +0x14(%ebp)           | int i_i             | argument 4 |

| +0x18(%ebp)           | long i_l            | argument 5 |

| +0x1c(%ebp)           | char *i_name        | argument 6 |

| +0x20(%ebp)           | struc_t *i_next     | argument 7 |

All arguments are passed on the stack.

A function locates its arguments based on its framepointer.

Arguments, even if smaller than 4 bytes in size, are 4-byte aligned on the stack.

How does a function return a value ?

Clear enough – the function epilogue places '1' into register **%eax**.

How is data in a compound (C struct) laid out, i.e. what padding if any is used ?

We can see from the instructions marked in **blue**, i.e. those that store the values passed as arguments into **init\_struc()** into the actual **struc\_t**, that the data structure is laid out so that members can be accessed *aligned at a multiple of their size*. After the leading **char s\_c**, one byte of padding makes sure that the following **unsigned short s\_us** starts at a 2-byte aligned address, and so on.

This is not mandated by the x86 architecture – as we can see e.g. from the instruction pointers, x86 has no generic problem with misaligned memory access.

So far, no thorough explanation of the *green* stuff, the function prologue/epilogue, has been given. We notice that it saves/restores the caller's framepointer and initializes the one for **init\_struc()**, which is needed to make argument access via **+...(%ebp)** possible, of course, but there's more to it.

The purpose of the prologue becomes clear when one looks at a significantly more complicated function. Let's take such an example from the Solaris kernel, in the form of the ufs filesystem implementation of VOP\_GETPAGE(). The disassembly starts with:

| ufs_getpage:     | pushl | %ebp              |

|------------------|-------|-------------------|

| ufs_getpage+0x1: | movl  | %esp,%ebp         |

| ufs_getpage+0x3: | subl  | \$0x58,%esp       |

| ufs_getpage+0x6: | andl  | \$0xfffffff8,%esp |

| ufs_getpage+0x9: | pushl | %ebx              |

| ufs_getpage+0xa: | pushl | %esi              |

| ufs_getpage+0xb: | pushl | %edi              |

and the function epilogue looks like this:

| ufs_getpage+0x861: | movl | -0x48(%ebp),%eax |

|--------------------|------|------------------|

| ufs_getpage+0x864: | popl | %edi             |

| ufs_getpage+0x865: | popl | %esi             |

| ufs_getpage+0x866: | popl | %ebx             |

| ufs_getpage+0x867: | movl | %ebp,%esp        |

| ufs_getpage+0x869: | popl | %ebp             |

| ufs_getpage+0x86a: | ret  |                  |

We see that in addition to stack reservation and framepointer initialization, the prologue also saves registers **%ebx**, **%esi** and **%edi** to the stack, while the function epilogue restores them before returning to the caller.